### **GOVERNMENT ARTS AND SCIENCE COLLEGE, KOMARAPALAYAM**

### **Department of Computer science**

## 17PCS02-Advanced Computer Architecture

UNIT - II

**Handled BY**

**K.SHANMUGA VADIVU**

# Pipelining and Superscalar Techniques

this chapted deals and pulped to the property of the property

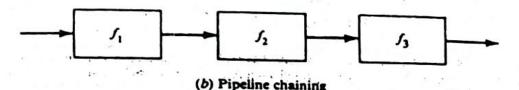

A linear pipeline processor is a cascade of processing stages which are linearly connected to perform a fixed function over a stream of data flowing from one end to the other. In modern computers, linear pipelines are applied for instruction execution, arithmetic computation, and memory-access operations.

## 6.1.1 Asynchronous and Synchronous Models

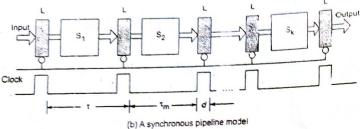

Allinear pipeline processor is constructed with k processing stages. External inputs (operands) are fed into the pipeline at the first stage  $S_i$ . The processed results are passed from stage  $S_i$  to stage  $S_{i+1}$ , for all i=1,2,....

1. The final result emerges from the pipeline at the last stage  $S_k$ .

Depending on the control of data flow along the pipeline, we model linear pipelines in two categories: asynchronous and syncnronous.

**Asynchronous Model** As shown in Fig. 6.1a, data flow between adjacent stages in an asynchronous pupeline is controlled by a handshaking protocol. When stage  $S_i$  is ready to transmit, it sends a ready signal to stage  $S_{i+1}$ . After stage  $S_{i+1}$  receives the incoming data, it returns an acknowledge signal to  $S_i$ .

Asynchronous pipelines are useful in designing communication channels in message-passing multicomliters where pipelined wormhole routing is practiced (see Chapter 9). Asynchronous pipelines may have a variable throughput rate. Different amounts of delay may be experienced in different stages.

S: = stage t = Clock period

tm = Maximum stage delay d = Latch delay Ack = Acknowledge signal

(c) Reservation table of a four-stage linear piceline

# Fig. 6.1 Two models of linear pipeline units and the corresponding reservation tal

Synchronous Model Synchronous pipelines are illustrated in Fig. 6.1b. Clocked tatches are used to interface between stages. The latches are made with master-slave flip-flops, which can isolate inputs from outputs. Upon the arrival of a clock pulse, all latches transfer data to the next stage simul:aneously,

The pipeline stages are combinational logic circuits. It is desired to have approximately equal delays in all stages. These delays determine the clock period and thus the speed of the pipeline. Unless otherwise specified, only synchronous pipelines are studied in this book.

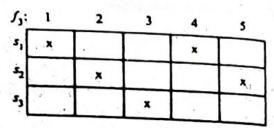

The utilization pattern of successive stages in a synchronous pipeline is specified by a reservation table. For a linear pipeline, the utilization follows the diagonal streamline pattern shown in Fig. 6.1c. This table is essentially a space-time diagram depicting the precedence relationship in using the pipeline stages. For 1 k-stage linear pipeline, k clock cycles are needed for data to flow through the pipeline.

Successive tasks or operations are initiated one per cycle to enter the pipeline. Once the pipeline is filled up, one result emerges from the pipeline for each additional cycle. This throughput is sustained only if the successive tasks are independent of each other.

sipelining and Superscalar Techniques

The state of the s

### 6.1.2 Clocking and Timing Control

The clark cycle  $\tau$  of a pipeline is determined below. Let  $\tau_i$  be the time delay of the circuitry in stages, and the time delay of a latch, as shown in Fig. 6.1b.

Clock Cycle and Throughput Denote the maximum stage delay as Tm, and we can write Tas

$$\tau = \max_{i} \left\{ \tau_{i} \right\}_{1}^{k} + d = \tau_{m} + d$$

At the rising edge of the clock pulse, the data is latched to the master flip-flops of each latch region. At the rising edge of the clock pairs, the rising edge of the clock pairs, the rising edge of the clock pairs,  $\tau_m >> d$  by one to two orders of magnitude. This implies the maximum stage delay  $\tau_m$  dominates the clock period.

The pipeline frequency is defined as the inverse of the clock period:

$$f = \frac{1}{\tau}$$

If one result is expected to come out of the pipeline per cycle, frepresents the maximum throughput of propeline. Depending on the initiation rate of successive tasks entering the pipeline, the actual through the pipeline may be lower than f. This is because more than one clock cycle has elapsed between sure task instintions.

Glock Skewing Ideally, we expect the clock pulses to arrive at all stages (latches) at the same However, due to a problem known as clock skewing, the same clock pulse may arrive at different stars. is time offset of c. Let tmax be the time delay of the longest logic path within a stage and tmin that of the the logic path within a stage.

To avoid a race in two successive stages, we must choose  $\tau_m \ge t_{max} + s$  and  $d \le t_{min} - s$ . These contents translate into the following bounds on the clock period when clock skew takes effect:

$$d + t_{max} + s \le \tau \le \tau_m + t_{min} - s$$

In the ideal case s = 0,  $t_{max} = \tau_m$ , and  $t_{min} = d$ . Thus, we have  $\tau = \tau_m + d$ , consistent with the definition Eq. 6.1 without the effect of clock skewing.

### 6.1.3 Speedup, Efficiency, and Throughput

ideally, a linear pipeline of k stages can process n tasks in k + (n-1) clock cycles, where k cycles are  $\infty$  complete the execution of the very first task and the remaining n-1 tasks require n-1 cycle is total time required is

$$T_k = [k + (n-1)]\tau$$

where t is the clock period. Consider an equivalent-function nonpipelined processor which has a flow delay of kt . The amount of time it takes to execute n tasks on this nonpipelined processor is I

Speedup Factor The speedup factor of a k-stage pipeline over an equivalent non pipelined cefined as

$$S_k = \frac{T_1}{T_k} = \frac{nk\tau}{k\tau + (n-1)\tau} = \frac{nk}{k + (n-1)}$$

129

The

tadt

5.2)

the

tcf

ive

me.

vith.

test

5.3) nin

lc:d the

ns -

The maximum throughput f occurs when  $E_k \to 1$  as  $n \to \infty$ . This coincides with the speedup definition The maximum through that  $H_k = E_{k'} f = E_{k'} \tau = S_{k'} k\tau$ . Other relevant factors of instruction pipelines will be given in Chapter 3. Note that  $H_k = E_{k'} f = E_{k'} \tau = S_{k'} k\tau$ . discussed in Chapters 12 and 13.

A dynamic pipeline can be reconfigured to perform variable functions at different times. The traditional linear pipelines are static pipelines because they are used to perform fixed functions.

A dynamic pipeline allows feedforward and feedback connections in addition to the streamline connections. For this reason, some authors call such a structure a nonlinear pipeline.

### 6.2.1 Reservation and Latency Analysis

In a static pipeline, it is relatively easy to partition a given function into a sequence of linearly ordered subfunctions. However, function partitioning in a dynamic pipeline becomes quite involved because the pipeline stages are interconnected with loops in addition to streamline connections.

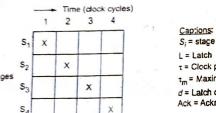

A multifunction dynamic pipeline is shown in Fig. 6.3a. This pipeline has three stages. Besides the streamline connections from  $S_1$  to  $S_2$  and from  $S_2$  to  $S_3$ , there is a feed forward connection from  $S_1$  to  $S_3$  and two feedback connections from  $S_3$  to  $S_2$  and from  $S_3$  to  $S_1$ .

These feedforward and feedback connections make the scheduling of successive events into the pipeline a nontrivial task. With these connections, the output of the pipeline is not necessarily from the last stage. In fact, following different dataflow patterns, one can use the same pipeline to evaluate different functions.

Reservation Tables The reservation table for a static linear pipeline is trivial in the sense that dataflow follows a linear streamline. The reservation table for a dynamic pipeline becomes more interesting because a nonlinear pattern is followed. Given a pipeline configuration, multiple reservation tables can be generated for the evaluation of different functions.

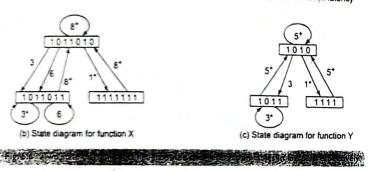

Two reservation tables are given in Figs. 6.3b and 6.3c, corresponding to a function X and a function Y, respectively. Each function evaluation is specified by one reservation table. A static pipeline is specified by a single reservation table. A dynamic pipeline may be specified by more than one reservation table.

Each reservation table displays the time-space flow of data through the pipeline for one function evaluation. Different functions follow different paths through the pipeline

Pipelining and Superscalar Techniques

The number of columns in a reservation table is called the evaluation time of a given function. For example, the function X requires eight clock cycles to evaluate, and function Y requires six cycles, as shown in Figs. 6.3b and 6.3c, respectively.

A pipeline initiation table corresponds to each function evaluation. All initiations to a static pipeline use the same reservation table. On the other hand, a dynamic pipeline may allow different initiations to follow a mix of reservation tables. The checkmarks in each row of the reservation table correspond to the time instants (cycles) that a particular stage will be used.

There may be multiple checkmarks in a row, which means repeated usage of the same stage in different cycles. Contiguous checkmarks in a row simply imply the extended usage of a stage over more than one cycle. Multiple checkmarks in a column mean that multiple stages need to be used in parallel during a particular clock cycle.

Latency Analysis The number of time units (clock cycles) between two initiations of a pipeline is the latency between them. Latency values must be nonnegative integers. A latency of k means that two initiations are separated by k clock cycles. Any attempt by two or more initiations to use the same pipeline stage at the same time will cause a collision.

A collision implies resource conflicts between two initiations in the pipeline. Therefore, all collisions must be avoided in scheduling a sequence of pipeline initiations. Some latencies will cause collisions, and some will not. Latencies that cause collisions are called forbidden latencies. In using the pipeline in Fig. 6.3 to evaluate the function X, latencies 2 and 5 are forbidden, as illustrated in Fig. 6.4.

|                       |    |                |                |                                 |                                 | _                               | - Time                                           |        |            |                |    |     |

|-----------------------|----|----------------|----------------|---------------------------------|---------------------------------|---------------------------------|--------------------------------------------------|--------|------------|----------------|----|-----|

|                       | 1  | 2              | 3              | 4                               | 5                               | 6                               | 7                                                | 8      | 9          | 10             | 11 |     |

| S <sub>1</sub>        | X1 |                | X <sub>2</sub> |                                 | X <sub>3</sub>                  | X <sub>1</sub>                  | X <sub>4</sub>                                   | X1. X2 |            | ×2. ×3         |    |     |

| Stages S <sub>2</sub> | -  | X <sub>1</sub> | -              | X <sub>1</sub> , X <sub>2</sub> |                                 | X <sub>2</sub> , X <sub>3</sub> |                                                  | X3, X4 |            | X <sub>4</sub> |    | ••• |

| S <sub>3</sub>        | -  |                | X <sub>1</sub> |                                 | X <sub>1</sub> , X <sub>2</sub> |                                 | X <sub>1</sub> , X <sub>2</sub> , X <sub>3</sub> | -10-1  | X2. X3. X4 |                |    |     |

(a) Collision with scheduling latency 2

|        |                |                |    |                |                | _              | → Tim                           | е              |       |                |                |    |

|--------|----------------|----------------|----|----------------|----------------|----------------|---------------------------------|----------------|-------|----------------|----------------|----|

|        |                | 1              | 2  | 3              | 4              | 5              | 6                               | 7              | 8     | 9              | 10             | 11 |

|        | Sı             | X <sub>1</sub> |    |                |                |                | X <sub>1</sub> , X <sub>2</sub> |                | X1    |                |                |    |

| Stages | S <sub>2</sub> |                | Х1 | 1.5            | X <sub>1</sub> |                |                                 | X <sub>2</sub> |       | X <sub>2</sub> |                |    |

|        | S <sub>3</sub> |                |    | X <sub>1</sub> |                | X <sub>1</sub> |                                 | X <sub>1</sub> | $x_2$ |                | X <sub>2</sub> |    |

(b) Collision with scheduling latency 5

The ith initiation is denoted as  $X_i$  in Fig. 6.4. With latency 2, initiations  $X_1$  and  $X_2$  collide in stage 2 at time 4. At time 7, these initiations collide in stage 3. Similarly, other collisions are shown at times 5, 6, 8, ..., etc.

The collision patterns for latency 5 are shown in Fig. 6.4b, where  $X_1$  and  $X_2$  are scheduled 5 clock cycles apart. Their first collision

To detect a forbidden latency, one needs simply to check the distance between any two checkmarks in the same row of the reservation table. For example, the distance between the first mark and the second mark in

Similarly, Intencies 2, 4, 5, and 7 are all seen to be forbidden from inspecting the same reservation table. row  $S_1$  in Fig. 6.3b is 5, implying that 5 is a forbidden latency.

From the reservation table in Fig. 6.3c, we discover the forbidden latencies 2 and z for function Y. A intency sequence is a sequence of permissible nonforbidden latencies between successive ask initiations.

A latency cycle is a latency sequence which repeats the same subsequence (cycle) indefinitely. Figure 6.5 illustrates latency cycles in using the pipeline in Fig. 8.340 evaluate the function X without causing a collision. For example, the latency cycle (1, 8) represents the unfinite latency sequence 1, 8, 1, 8, .... This implies that successive initiations of new tasks are separated by one cycle and eight cycles alternately.

| X <sub>1</sub>   X <sub>2</sub>   X <sub>1</sub>   X <sub>2</sub>   X <sub>3</sub>   X <sub>4</sub>   X <sub>3</sub>   X <sub>4</sub>   X <sub>5</sub>   X <sub>5</sub>   X <sub>5</sub>   X <sub>5</sub>   X <sub>5</sub>   X <sub>6</sub>   X <sub>7</sub>   X <sub>7</sub> | 1 2                           | 3   | 4              | 5    | 6     | 7            | 8        | 9    | 10  | 11    | 12  | 13             | 14   | 15<br>X <sub>2</sub> | 16<br>X | X, | 18<br>X4 | X5  | 20<br>1×6 | Ė   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|----------------|------|-------|--------------|----------|------|-----|-------|-----|----------------|------|----------------------|---------|----|----------|-----|-----------|-----|

| $X_1 X_2 X_1 X_1 X_2 X_2 X_3 X_4 X_3 X_4 X_3 X_6 X_6 X_6 X_6 X_6 X_6 X_6 X_6 X_6 X_6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | X <sub>1</sub> X <sub>2</sub> |     | V .            | N.   | X,    | X2           | X,       | X2   | 1,3 | X     | Xe  | X <sub>3</sub> | X,   | 3                    |         |    |          |     | X5        |     |

| (a) Latericy cycle (1, 8) = 1, 8, 1, 8, 1, 8,, with an average latericy of 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | - 71                          | -   | ~4             | -    | Н     | Y            | Υ.       |      |     | 1     | X., | X              | X.3  |                      | X3      |    |          |     |           |     |

| Cycle repeats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 4                           | ĸ.I | Kni            | 200  |       | The state of | (100.00) |      | 9 ( | 1     |     |                |      | _                    | _       | _  |          |     |           |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                               | Χ,  | X <sub>2</sub> | A    | _     | ~4           | * 4      | _    |     |       | -   | wit            | h ai | 181                  | era     | ge | ate      | ncy | of 4      | 1.5 |

| 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (a) Late                      | noy | Cyc            | ie i | 7. 8  | 0 =          | 1, 8     | . 1. | 18, | 1, 8, |     | wit            | h ar | 84                   | era     | ge | late     | ncy | of 4      | 1.5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (a) Later                     | noy | Cyc            | ie i | 73. 2 | 3 =          | 1. 8     |      |     |       |     |                | h ar | 8                    | era     | ge | ate      | ncy | of 4      | 1.5 |

|     | 9 | 2 | 2  | ·  | 6  | 7  | 8  | 9   | 10 | 11 | 12 | 13 | 14             | 15 | 16 | -7             | 18             | 19 | 20             |

|-----|---|---|----|----|----|----|----|-----|----|----|----|----|----------------|----|----|----------------|----------------|----|----------------|

| V   | * | - | W. | ~  | X. | X. | X. | X-  | X, | Xn | Xq | X, | X <sub>3</sub> | X4 | Xs | X              | X5             | X7 | X5             |

| Ng. | - | - | 2  | ~  | -  | 3  | x. | -   | X. | X. |    | X. | Xe             | 1  | X  | X <sub>s</sub> | Г              | Xs | X <sub>7</sub> |

| - 3 | 4 | 2 | Ag | ×2 | W  | ×2 | Y  | 26. | Y. | χ_ | X. | X. | X,             | Xe | X, | X6             | X <sub>6</sub> | Χe | Χę             |

| -  | 2  | 3  | 4 | 5  | 6  | 7  | 2   | 9   | 10  | 11 | 12 | 13 | 14  | 15 | 16 | 17 | 18             | 19 | 20  | 2  |

|----|----|----|---|----|----|----|-----|-----|-----|----|----|----|-----|----|----|----|----------------|----|-----|----|

| X. |    |    |   |    | X, | X2 | X.  |     |     |    | X2 | X3 | X-2 |    |    |    | X <sub>3</sub> | X, | X3  | Γ  |

|    | X, |    | X |    |    |    | X.2 |     | X.2 |    | -  |    | Х,  | ٠. | X3 |    |                |    | X4  | ٦, |

|    |    | X, |   | X, |    | X, |     | 1,2 |     | X2 | -  | X  |     | X3 | X  |    | X <sub>3</sub> |    | X.3 | _  |

The average latency of a latency cycle is obtained by dividing the sum of all latencies by the number of latencies along the cycle. The latency cycle (1, 8) thus has an average latency cf (1 + 8)/2 = 4.5. A constant cycle is a latency cycle which contains only one latency value. Cycles (3) and (6) in Figs. 6.5b and 6.5c are both constant cycles. The average latency of a constant cycle is simply the latency itself. In the next section, we describe how to obtain these latency cycles systematically.

Pipe ining and Superscalar Techniques

The state of the s

### 6.2.2 Collision-Free Scheduling

When scheduling events in a nonlinear pipeline, the main objective is to obtain the shortest average collisions. In what follows, we present a systematic and the shortest average collisions. When scheduling events in a nonlinear pipeline, between initiations without causing collisions. In what follows, we present a systematic method for the collisions without causing collisions.

the collision-free scheduling.

We study below collision vectors, state diagrams, single cycles, greedy cycles, and which sineline design theory was originally developed by Davidson (1971) and the sineline design theory was originally developed by Davidson (1971). We study below collision vectors, state diagrams, and developed by Davidson (1971) and a latency (MAL). This pipeline design theory was originally developed by Davidson (1971) and a latency (MAL).

Collision Vectors By examining the reservation table, one can distinguish the set of Personal Port a reservation table with n columns, the maximum table with n columns, the maximum table with n columns to the maximum table with n columns table wi Collision Vectors By examining the reservation table with n columns, the maximum forbidden latencies. For a reservation table with n columns, the maximum forbidden latencies is a character of the character of t from the set of forbidden latencies. For a rose  $m \le m - 1$ . The permissible latency p should be as small as possible. The choice is made in the set of forbidden latency p should be as small as possible. The choice is made in the set of forbidden latency p should be as small as possible.

A permissible latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. In theory, a latency of p = 1 corresponds to the ideal case. A permissible latency of p-1 correspond schieved in a static pipeline which follows a linear (diagonal or streamlined) reservation that it is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which follows a linear (diagonal or streamlined) reservation that is a static pipeline which is a static pi

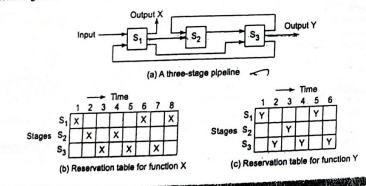

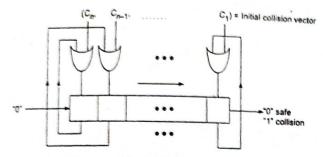

The combined set of permissible and forbidden latencies can be easily displayed by which is an *m*-bit binary vector  $C = (C_m C_{m-1} ... C_2 C_1)$ . The value of  $C_i = 1$  if latency which is an m-bit binary vector  $C_{m-m-1}$  and  $C_{i} = 0$  if latency i is permissible. Note that it is always true that  $C_{m} = 1$ , corresponding to

For the two reservation tables in Fig. 6.3, the collision vector  $C_X = (1011010)$  is obtaining and  $C_Y = (1010)$  for function Y. From  $C_X$ , we can immediately tell that latencies 7, 5,4,  $\frac{1}{2}$ and latencies 6, 3, and 1 are permissible. Similarly, 4 and 2 are forbidden latencies and 3 and 2 are latencies for function Y.

State Diagrams From the above collision vector, one can construct a state days permissible state transitions among successive initiations. The collision vector, like Crame the initial state of the pipeline at time 1 and thus is called an initial collision vector Language latency within the range  $1 \le p \le m-1$ .

The next state of the pipeline at time t+p is obtained with the assistance of an m-bit next state. in Fig. 6.6a. The initial collision vector C is initially loaded into the register. The register states right. Each 1-bit shift corresponds to an increase in the latency by 1. When a 0 bit emenes im an efter p shifts, it means p is a permissible latency. Likewise, a 1 bit being shifted our means thus the corresponding latency should be forbidden.

Logical 0 enters from the left end of the shift register. The next state after p states a me bitwise-ORing the initial collision vector with the shifted register contents. For example state  $C_r = (1011010)$ , the next state (1111111) is reached after one right shift of the region, where (1011011) is reached after three shifts or six shifts.

Example 6.2 The state transition diagram for a pipe

A state diagram is obtained in Fig. 6.6b for function X. From the initial state (1011010), with transitions are possible transitions are possible, corresponding to the three permissible latencies 6, 3, and limits vector. Similarly, from vector. Similarly, from state (1011011), one reaches the same state after either three sinks of 2.8

7

-10

C

ra then an iti

When the number of shifts is m + 1 or greater, all transitions are redirected back to the initial state. For example, after eight or more (denoted as  $8^+$ ) shifts, the next state must be the initial state, regardless of which state the transition starts from. In Fig. 6.6c, a state diagram is obtained for the reservation table in Fig. 6.3c using a 4-bit shift register. Once the initial collision vector is determined, the corresponding state diagram is uniquely determined.

(a) State transition using an n-bit right shift register, where n is the maximum forbidden latency

The 0's and 1's in the present state, say at time t, of a state diagram indicate the permissible and forbidden latencies, respectively, at time t. The bitwise ORing of the shifted version of the present state with the initial collision vector is meant to prevent collisions from future initiations starting at time t+1 and onward.

Thus the state diagram covers all permissible state transitions that avoid collisions. All latencies equal to or greater than m are permissible. This implies that collisions can always be avoided if events are scheduled far apart (with latencies of  $m^+$ ). However, such long latencies are not tolerable from the viewpoint of pipeline throughput.

Greedy Cycles From the state diagram, we can determine optimal latency cycles which result in the MAL. There are infinitely many latency cycles one can trace from the state diagram. For example, (1, 8), (1, 8, 6, 8), (3), (6), (3, 8), (3, 6, 3) ..., are legitimate cycles traced from the state diagram in Fig. 6.6b. Among these cycles, only simple cycles are of interest.

A simple cycle is a latency cycle in which each state appears only once. In the state diagram in Fig. 6.6b, only (3), (6), (8), (1, 8), (3, 8), and (6, 8) are simple cycles. The cycle (1, 8, 6, 8) is not simple because it travels through the state (1011010) twice. Similarly, the cycle (3, 6, 3, 8, 6) is not simple because it repeats the state (1011011) three times.

Some of the simple cycles are greedy cycles. A greedy cycle is one whose edges are all made with minimum latencies from their respective starting states. For example, in Fig. 6.6b the cycles (1, 8) and (3) are greedy cycles. Greedy cycles in Fig. 6.6c are (1, 5) and (3). Such cycles must first be simple, and their average latencies must be lower than those of other simple cycles. The greedy cycle (1, 8) in Fig. 6.6b has an average latency of (1 + 8)/2 = 4.5, which is lower than that of the simple cycle (6, 8) = (6 + 8)/2 = 7. The greedy cycle (3) has a constant latency which equals the MAL for evaluating function X without causing a collision.

The MAL in Fig. 6.6c is 3, corresponding to either of the two greedy cycles. The minimum-latency edges in the state diagrams are marked with asterisks.

At least one of the greedy cycles will lead to the MAL. The collision-free scheduling of pipeline events is thus reduced to finding greedy cycles from the set of simple cycles. The greedy cycle yielding the MAL is the final choice.

### 5.2.3 Pipeline Schedule Optimization

An optimization technique based on the MAL is given below. The idea is to insert noncompute delay stages into the original pipeline. This will modify the reservation table, resulting in a new collision vector and an improved state diagram. The purpose is to yield an optimal latency cycle, which is absolutely the shortest.

Bounds on the MAL In 1972, Shar determined the following bounds on the minimal average latency (MAL) achievable by any control strategy on a statically reconfigured pipeline executing a given reservation table:

- The MAL is lower-bounded by the maximum number of checkmarks in any row of the reservation table.

- (2) The MAL is lower than or equal to the average latency of any greedy cycle in the state diagram.

- (3) The average latency of any greedy cycle is upper-bounded by the number of 1's in the initial collision vector plus 1. This is also an upper bound on the MAL.

Interested readers may refer to Shar (1972) or find proofs of these bounds in Kogge (1981). These results suggest that the optimal latency cycle must be selected from one of the lowest greedy cycles. However, a greedy cycle is not sufficient to guarantee the optimality of the MAL. The lower bound guarantees the optimality. For example, the MAL = 3 for both function X and function Y and has met the lower bound of 3 from their respective reservation tables.

From Fig. 6.6b, the upper bound on the MAL for function X is equal to 4 + 1 = 5, a rather loose bound. On the other hand, Fig. 6.6c shows a rather tight upper bound of 2 + 1 = 3 on the MAL. Therefore, all greedy cycles for function Y lead to the optimal latency value of 3, which cannot be lowered further.

To optimize the MAL, one needs to find the lower bound by modifying the reservation table. The approach is to reduce the maximum number of checkmarks in any row. The modified reservation table must preserve the original function being evaluated. Patel and Davidson (1976) have suggested the use of noncompute delay stages to increase pipeline performance with a shorter MAL. Their technique is described below.

a constant conclusion. The relationship between the two measures is a function of the reservation table and At least over stage of the papeline about the fully (100%) utilized at the steady state in any acceptable integers over some or one paperine amount re runy (1909a) uninteed at the steamy state in any acceptance integers of the paperine capability has not been fully explored. In such cases, the initiation

cycle may not be optimal and another initiation cycle should be examined for improvement.

A stream of instructions can be executed by a pupeline in an overlapped manner. We describe INSTRUCTION PIPELINE DESIGN below instruction pipelines for CISC and RISC scalar processors. Topics to be studied include

morneties prefer hing, case forwarding, becard evolutions, interferking for resolving data dependences, dynamic instruction scheduling, and branch handling techniques for improving pipeline3 processor performance. Further discussion on instruction level parallelism will be found in Chapter 12

A reports instruction execution consists of a sequence of operations, including instruction fetch, decode, 6.3.1 Instruction Execution Phases operand feeth, execute, and write-back phases. These phases are ideal for everlapped execution or, a linear

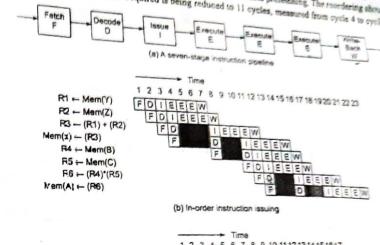

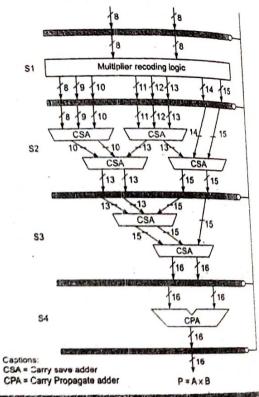

Pipelines instruction Processing Applical instruction pipeline is depicted in Fig. 6.9. The feich stage (F) feeches instructions from a cache memory, ideally one per cycle. The decode stage (D) reveals the instruction function to be performed and identifies the resources needed. Resources include general-purpose registers, busies, and functional units. The issue stope (1) reserves resources. The operands are also read from registers

The instructions are executed at our or several execute stages (E). Three execute stages are shown in during the issue stage Fig. 6.%. The last writeback stops (W) is used to write results into the registers. Memory load or store operations are treated as part of execution. Figure 6.9 shows the flow of machine instructions through a typical papeline. These eight instructions are for pipelined execution of the high-level language statements X = Y + Z and  $A = B \times C$ . Here we have assumed that load and store instructions take four execution clock cycles, while floating-point and multiply operations take three cycles.

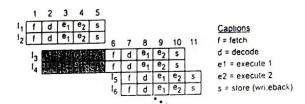

The above timing assumptions represent typical values found in an older CISC processor. In many RISC processors, fewer clock cycles are mended. On the other hand, Cray I required 11 cycles for a load and a floating-point addition took six. With in-order instruction issuing, if an instruction is blocked from issuing due to a data or resource dependence, all instructions following it are blocked

Figure 6.96 illustrates the issue of instructions following the original program order. The shaded boxes correspond to idie cycles when instruction issues are blocked due to resource latericy or conflicts or due to data dependences. The first two load instructions issue on consecutive cycles. The add is dependen: on both loads and exust went three cycles before the data (Y and Z) are loaded in.

Similarly, the store of the sum to memory location X must wait three cycles for the add to fin.sh due to a flow dependence. There are similar blockages during the calculation of A. The total time required is 17 clock cycles. This time is measured beginning at cycle 4 when the first instruction starts execution until cycle 20 Pigeliniag and Superscolor Fechniques

when the last instruction starts execution. This timing measure eliminates the undue effects of the president

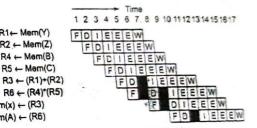

Figure 5.9e shows an improved timing after the instruction issuing order is changed to elifations unnecessary delays due to dependence. The idea is to issue all four load operations in the beginning. Both in odd and multiply instructions are blocked fewer cycles due to this data prefetching. The reordering should not change the end results. The time required is being reduced to 11 cycles, measured from cycle 4 to cycle 14.

R1← Mem(Y)

$R2 \leftarrow Mem(Z)$

R4 ← Mem(B)

R5 ← Mem(C)

$Mem(x) \leftarrow (R3)$

$Mam(A) \leftarrow (R6)$

(c) Reordered instruction issuing

# Example 6.4 The MIPS R4000 instruction pipeline

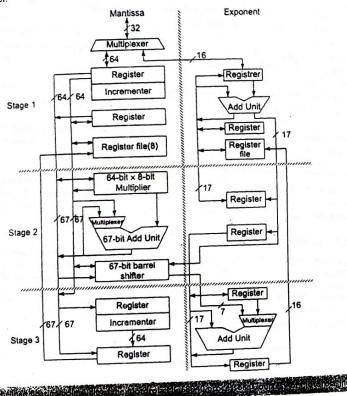

The MIPS R4CO was a pipelined 64-bit processor using separate instruction and data cache at a stage pipeline for executing register-based instructions. As illustrated in Fig. 6.10, the process design was targeted to achieve an execution rate approaching one instruction per cycle.

Instruction DF: Data first IS: Instruction second cache DS: Data second RF: Register file Instruction access EX: Execution tao check TC: Tag check IF: Instruction first WB: Write back Instruction address Instruction translation decode Read ALU (D-cache register operation Data tag Write to check register Data address translation I-cache Decode Register Registe (a) R4000 pipeline stages

Master

clock cycle

| Eight deep

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| Pipeline cycle

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

| IF IS RF EX DF DS TC WB

† Current CPU cycle

(b) R4000 instruction overlapping in pipeline

The execution of each R4000 instruction consisted of eight major steps as summarized in Fig. 6.10a. Each of these steps required approximately one clock cycle. The instruction and data memory references are split across two stages. The single-cycle ALU stage took slightly more time than each of the cache access stages.

The overlapped execution of successive instructions is shown in Fig. 6.10b. This pipeline operated efficiently because different CPU resources, such as address and bus access, ALU operations, register accesses, and so on, were utilized simultaneously on a noninterfering basis.

The internal pipeline clock rate (100 MHz) of the R4000 was twice the external input or master clock

frequency. Figure 6.10b shows the optimal pipeline movement, completing one instruction every internal clock cycle. Load and branch instructions introduce extra delays.

### 06.3.2 Mechanisms for Instruction Pipelining

We introduce instruction buffers and describe the use of cacheing, collision avoidance, multiple functional units, register tagging, and internal forwarding to smooth pipeline flow and to remove bottlenecks and unnecessary memory access operations.

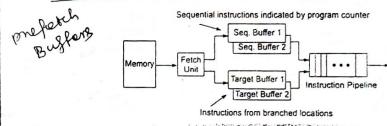

Prefetch Buffers Three types of buffers can be used to match the instruction fetch rate to the pipeline consumption rate. In one memory-access time, a block of consecutive instructions are fetched into a prefetch buffer as illustrated in Fig. 6.11. The block access can be achieved using interleaved memory modules or using a cache to shorten the effective memory-access time as demonstrated in the MIPS R4000.

Fig. 6.11 The user of seminal and carries buffers

Sequential instructions are loaded into a pair of sequential buffers for in-sequence pipelining. Instructions from a branch target are loaded into a pair of target buffers for out-of-sequence pipelining. Both buffers operate in a first-in-first-out fashion. These buffers become part of the pipeline as additional stages.

A conditional branch instruction causes both sequential buffers and target buffers to fill with instructions. After the branch condition is checked, appropriate instructions are taken from one of the two buffers, and instructions in the other buffer are discarded. Within each pair, one can use one buffer to load instructions from memory and use another buffer to feed instructions into the pipeline. The two buffers in each pair alternate to prevent a collision between instructions flowing into and out of the pipeline.

A third type of prefetch buffer is known as a loop buffer. This buffer holds sequential instructions contained in a small loop. The loop buffers are maintained by the fetch stage of the pipeline. Prefetched instructions in the loop body will be executed repeatedly until all iterations complete execution. The loop buffer operates in two steps. First, it contains instructions sequentially ahead of the current instruction. This saves the instruction fetch time from memory. Second, it recognizes when the target of a branch falls within the loop boundary. In this case, unnecessary memory accesses can be avoided if the target instruction is already in the loop buffer. The CDC 6600 and Cray 1 made use of loop buffers.

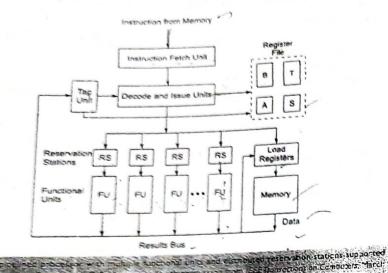

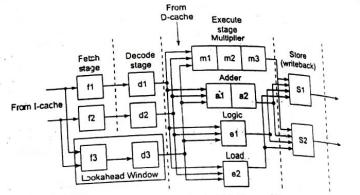

Multiple Functional Units Sometimes a certain pipeline stage becomes the bottleneck. This stage corresponds to the row with the maximum number of checkmarks in the reservation table. This bottleneck problem can be alleviated by using multiple copies of the same stage simultaneously. This leads to the use of multiple execution units in a pipelined processor design (Fig. 6.12).

The state of the s

Salar de State

Sobi (1990) used a model architecture for a pipelined scalar processor containing multiple functional units

Sobi (1990) used a model architecture for a pipelined scalar processor containing multiple tactions (Fig. 6.12). In order to resolve data or resource dependences among the successive instructions entering the pipeline, the reservation stations (RS) are used with each functional unit. Operations wait in the RS until pipeline, the reservation stations (RS) are used with each functional unit. Operations wait in the RS until their data dependences have been resolved. Each RS is uniquely identified by a tag, which is menitored by a tag unit.

The tag unit keeps checking the tags from all currently used registers or RSs. This register tagging technique allows the hardware to resolve conflicts between source and destination registers assigned for multiple instructions. Besides resolving conflicts, the RSs also serve as buffers to interface the pipelined functional units with the decode and issue units. The multiple functional units operate in parallel, once the dependences are resolved. This alleviates the bottleneck in the execution stages of the instruction pipeline.

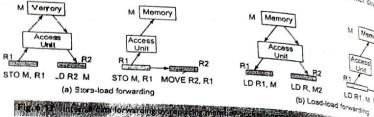

Internal Data Forwarding The throughput of a pipelined processor can be further improved with internal data forwarding among multiple functional units. In some cases, some memory-access operations can be replaced by register transfer operations. The idea is described in Fig. 6.13.

A store-load forwarding is shown in Fig. 6.13a in which the load operation (LD R2, M from memory to register R2 can be replaced by the move operation (MOVE R2, R1) from register R1 to register R2. Since register transfer is faster than memory access, this data forwarding will reduce memory traffic and thus results in a shorter execution time. Similarly, load-load forwarding (Fig. 6.13b) eliminates the second

Reckning and Superscalar echniques

iond operation (LD R2, M) and replaces it with the move operation (MOVE R2, R1). Further discuss

(P)

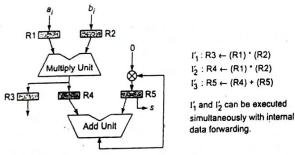

# Example 6.5 Implementing the dot-product operation with an add unit

One can feed the output of a multiplier directly to the input of an adder (Fig. 6.14) for implemental following dot-product operation:

$$s = \sum_{i=1}^{n} a_i \times b_i$$

Without internal data forwarding between the two functional units, the three instructors sequentially executed in a looping structure (Fig. 6.14a). With data forwarding, the output of the field directly into the input register R4 of the adder (Fig. 6.14b). At the same time, the output of the is also revited to register R3. Internal data forwarding between the two functional units thus reduce the execution time through the pipelined processor.

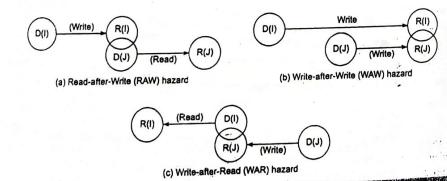

Hazard Avoidance The read and write of shared variables by different instructions in a present to different results if these instructions are executed out of order. As illustrated in Fig. 6.15, the logic hazards are possible.

Consider two instructions I and J. Instruction J is assumed to logically follow instruction program order. If the actual execution order of these two instructions violates the program order results may be read or written, thereby producing hazards.

Hazards should be prevented before these instructions enter the pipeline, such as by holding the function of an instruction I is resolved. We use the notation D(I) and R(I) for the domain at the following of an instruction I.

The comain cortains the input set (such as operands in registers or in memory) to be used by

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which

The range corresponds to the output set of instruction I. Listed below are conditions under which it is the output set of instruction I. Listed below are conditions under which it is the output set of instruction I. Listed below are conditions under which it is the output set of instruction I. Listed below are conditions under which it is the output set of its listed below are conditions.

Pipelining and Superscalar Techniques

built in the CDC 6600 processor.

45

**R2**

th

b

he

C)

be

tal

зd

of

10

::1

(a) Without data forwarding

(b) With internal data forwarding

$R(I) \cap D(J) \neq \phi$  for RAW hazard  $R(I) \cap R(J) \neq \emptyset$  for WAW hazard (6.11) $D(I) \cap R(J) \neq \phi$  for WAR hazard

These conditions are necessary but not sufficient. This means the hazard may not appear even if one or more of the conditions exist. The RAW hazard corresponds to the flow dependence, WAR to the antidependence, and WAW to the output dependence introduced in Section 2.1. The occurrence of a logic hazard depends on the order in which the two instructions are executed. Chapter 12 discusses techniques to handle such hazards.